Hak Desain Tata Letak Sirkuit Terpadu

Contoh hak desain tata letak sirkuit terpadu – Di era digital yang serba terhubung ini, sirkuit terpadu (IC) menjadi tulang punggung berbagai perangkat elektronik, dari smartphone hingga superkomputer. Perlindungan hukum atas desain tata letak IC, yang seringkali merupakan hasil riset dan pengembangan yang intensif, sangat krusial. Hak Desain Tata Letak Sirkuit Terpadu (HDTL-IC) hadir sebagai payung hukum untuk melindungi investasi dan inovasi di bidang ini.

Mari kita bahas lebih dalam mengenai hak ini.

Definisi Hak Desain Tata Letak Sirkuit Terpadu

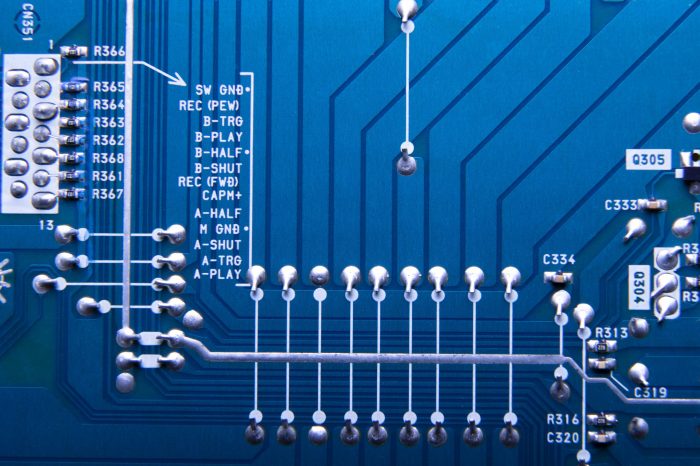

Hak Desain Tata Letak Sirkuit Terpadu (HDTL-IC) adalah hak eksklusif yang diberikan kepada pembuat desain tata letak sirkuit terpadu atas karya ciptaannya. Ini melindungi topografi tiga dimensi dari sirkuit terpadu, termasuk susunan elemen-elemennya, interkoneksi, dan elemen-elemen lainnya yang diperlukan untuk pengoperasiannya. Hak ini bukan sekedar melindungi tampilan visual, tetapi juga fungsi dan struktur internal IC yang menentukan performanya.

Dengan kata lain, HDTL-IC melindungi ide inovatif yang diwujudkan dalam bentuk fisik sirkuit terpadu, mencegah peniruan tanpa izin.

Perbedaan HDTL-IC dengan Hak Kekayaan Intelektual Lainnya

HDTL-IC berbeda dengan hak kekayaan intelektual lainnya seperti paten dan hak cipta. Paten melindungi invensi atau penemuan baru yang bersifat fungsional, sedangkan hak cipta melindungi karya sastra dan seni. HDTL-IC fokus pada topografi tiga dimensi dari sirkuit terpadu, melindungi arsitektur fisik dan susunan elemen-elemennya, bukan fungsi atau prinsip kerja yang mendasarinya.

Perbedaan ini penting untuk memahami cakupan perlindungan yang diberikan oleh masing-masing jenis hak kekayaan intelektual.

Contoh Kasus Pelanggaran Hak Desain Tata Letak Sirkuit Terpadu

Bayangkan sebuah perusahaan telah berinvestasi besar dalam merancang sebuah chip memori canggih dengan arsitektur unik. Sebuah perusahaan lain kemudian memproduksi chip memori dengan topografi tiga dimensi yang hampir identik, tanpa izin. Ini merupakan pelanggaran HDTL-IC. Akibatnya, perusahaan pertama dapat menuntut perusahaan kedua atas kerugian yang diderita akibat peniruan tersebut, termasuk kehilangan pendapatan dan reputasi.

Perbandingan HDTL-IC dengan Paten

| Nama Hak KI | Objek Perlindungan | Syarat Perlindungan | Durasi Perlindungan |

|---|---|---|---|

| Hak Desain Tata Letak Sirkuit Terpadu (HDTL-IC) | Topografi tiga dimensi sirkuit terpadu | Keaslian dan kebaruan desain | 10 tahun sejak tanggal pengajuan permohonan |

| Paten | Invensi atau penemuan baru yang bersifat fungsional | Kebaruan, langkah inventif, dan penerapan industri | 20 tahun sejak tanggal pengajuan permohonan |

Elemen-elemen Penting yang Dilindungi HDTL-IC

HDTL-IC melindungi berbagai elemen penting dalam desain tata letak sirkuit terpadu. Ini termasuk susunan elemen-elemen aktif dan pasif, interkoneksi antar elemen, struktur lapisan-lapisan, dan elemen-elemen lainnya yang membentuk topografi tiga dimensi IC. Perlindungan ini tidak meliputi ide atau prinsip kerja yang mendasari fungsi IC, tetapi fokus pada wujud fisik dari desain tersebut.

Dengan demikian, perusahaan yang memiliki HDTL-IC dapat mencegah peniruan yang menyalin struktur fisik IC mereka.

Perlindungan Hukum Hak Desain Tata Letak Sirkuit Terpadu: Contoh Hak Desain Tata Letak Sirkuit Terpadu

Di era digital yang serba cepat ini, perlindungan kekayaan intelektual, khususnya untuk inovasi teknologi, menjadi semakin krusial. Desain tata letak sirkuit terpadu (IC), jantung dari berbagai perangkat elektronik modern, tak terkecuali. Memahami perlindungan hukum yang menaungi hak desain tata letak sirkuit terpadu di Indonesia sangat penting bagi para inovator dan pelaku industri untuk mencegah pembajakan dan melindungi investasi mereka.

Prosedur Pendaftaran Hak Desain Tata Letak Sirkuit Terpadu di Indonesia

Pendaftaran hak desain tata letak sirkuit terpadu di Indonesia dilakukan melalui Direktorat Jenderal Kekayaan Intelektual (DJKI) Kementerian Hukum dan Hak Asasi Manusia. Prosesnya melibatkan beberapa tahapan, mulai dari persiapan dokumen hingga penerbitan sertifikat. Ketelitian dan pemahaman prosedur yang tepat akan memaksimalkan peluang keberhasilan pendaftaran.

Sanksi bagi Pelanggar Hak Desain Tata Letak Sirkuit Terpadu, Contoh hak desain tata letak sirkuit terpadu

Pelanggaran hak desain tata letak sirkuit terpadu dapat berakibat fatal bagi pelakunya. Undang-undang memberikan sanksi tegas berupa denda dan hukuman penjara, bertujuan memberikan efek jera dan melindungi hak-hak pemegang hak cipta. Besarnya sanksi bervariasi tergantung pada tingkat pelanggaran dan kerugian yang ditimbulkan.

Contoh Kasus Sengketa Hak Desain Tata Letak Sirkuit Terpadu

Meskipun sulit untuk menemukan detail spesifik kasus sengketa yang dipublikasikan secara terbuka karena kerahasiaan data dan pertimbangan bisnis, kita bisa membayangkan skenario umum. Misalnya, perusahaan A menggugat perusahaan B karena dianggap telah meniru desain tata letak sirkuit terpadu milik A yang telah terdaftar. Pengadilan akan meneliti kesamaan desain, bukti kepemilikan, dan kerugian yang dialami perusahaan A untuk menentukan putusan.

Putusan pengadilan dapat berupa perintah penghentian produksi dan penjualan produk yang melanggar, serta pembayaran ganti rugi.

Langkah-Langkah Pendaftaran Hak Desain Tata Letak Sirkuit Terpadu

- Mempersiapkan dokumen yang dibutuhkan, termasuk spesifikasi teknis desain tata letak sirkuit terpadu.

- Mengisi formulir pendaftaran yang tersedia di DJKI.

- Melakukan pembayaran biaya pendaftaran.

- Menyerahkan dokumen dan formulir pendaftaran ke DJKI.

- Menunggu proses pemeriksaan dan verifikasi oleh DJKI.

- Penerbitan sertifikat hak desain tata letak sirkuit terpadu setelah lolos verifikasi.

Alur Diagram Pendaftaran Hak Desain Tata Letak Sirkuit Terpadu

Proses pendaftaran dapat divisualisasikan sebagai alur berikut: Pertama, persiapan dokumen dan formulir. Kedua, pengajuan ke DJKI disertai pembayaran biaya. Ketiga, proses pemeriksaan dan verifikasi oleh DJKI. Terakhir, penerbitan sertifikat jika semua persyaratan terpenuhi. Setiap tahap memiliki tenggat waktu yang perlu diperhatikan agar proses berjalan lancar.

Saudara-saudara, mari kita bicara tentang perlindungan hak cipta! Contoh hak desain tata letak sirkuit terpadu sangat penting, seperti halnya keindahan arsitektur. Bayangkan detail rumitnya, sehalus desain sirkuit yang kompleks. Begitu pula dengan keindahan spiritual yang terpancar dari sebuah masjid, khususnya dari mihrabnya.

Lihatlah contoh yang mengagumkan ini, dengan desain minimalis yang elegan: contoh desain mihrab masjid minimalis. Ketelitian dan keindahan, baik dalam teknologi maupun seni religi, sama-sama membutuhkan perlindungan hak cipta yang kuat. Oleh karena itu, mari kita hargai karya kreator dan lindungi hak desain tata letak sirkuit terpadu kita!

Konsultasi dengan konsultan kekayaan intelektual dapat membantu mempercepat dan mempermudah proses ini.

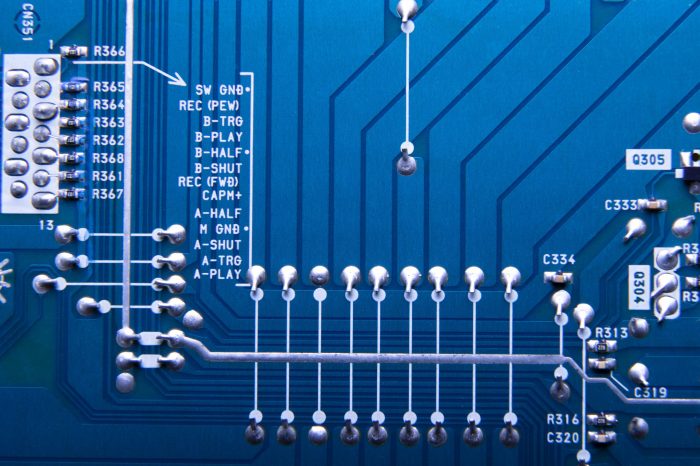

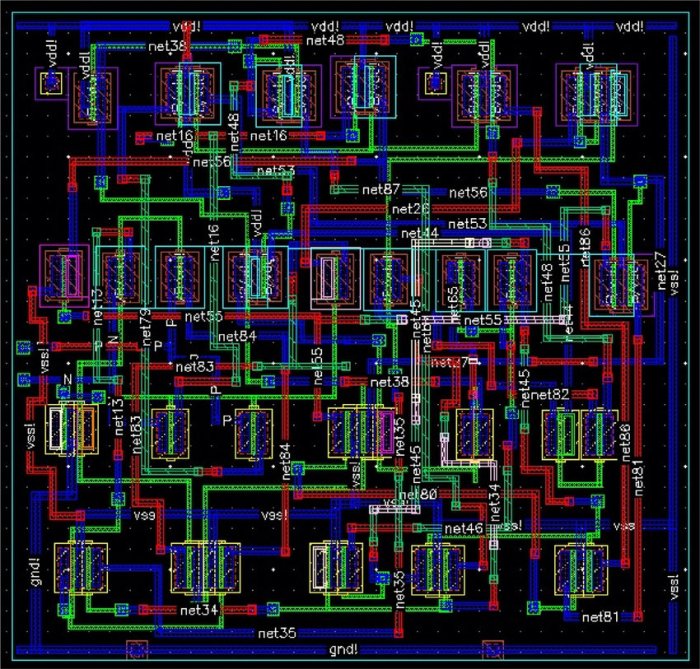

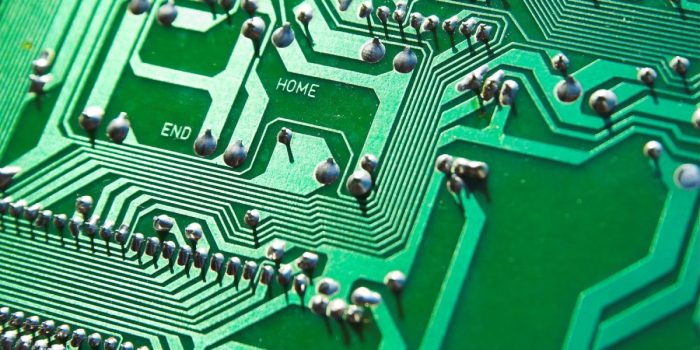

Aspek Teknis Desain Tata Letak Sirkuit Terpadu

Desain tata letak sirkuit terpadu (IC layout) merupakan jantung dari sebuah chip semikonduktor. Kualitas desain ini secara langsung berdampak pada performa, daya, dan biaya produksi IC. Pemahaman mendalam tentang berbagai aspek teknis sangat krusial untuk menghasilkan IC yang handal dan efisien. Berikut ini akan dibahas beberapa aspek kunci dalam desain tata letak sirkuit terpadu.

Topologi Desain Tata Letak Sirkuit Terpadu

Topologi desain tata letak IC mengacu pada pengaturan fisik komponen-komponen di atas substrat silikon. Pemilihan topologi yang tepat sangat penting untuk optimasi kinerja dan area chip. Ada beberapa topologi umum yang digunakan, masing-masing dengan kelebihan dan kekurangannya sendiri.

- Topologi Standar Sel: Metode ini menggunakan sel-sel standar yang telah dirancang sebelumnya dan disusun secara teratur. Cocok untuk desain digital yang besar dan kompleks, karena memungkinkan penggunaan kembali komponen dan mempercepat proses desain.

- Topologi Gate Array: Topologi ini menggunakan array gate yang sudah terpasang sebelumnya, dan interkoneksi antar gate dikonfigurasi sesuai dengan desain yang diinginkan. Lebih fleksibel daripada standar sel, tetapi mungkin kurang efisien dalam hal area.

- Topologi Full Custom: Dalam topologi ini, setiap komponen dirancang dan ditempatkan secara individual. Memberikan fleksibilitas maksimum dan optimasi kinerja, namun membutuhkan waktu dan biaya yang signifikan, cocok untuk desain high-performance dan aplikasi khusus.

Perbedaan Desain Tata Letak Sirkuit Terpadu Analog dan Digital

Desain tata letak untuk sirkuit analog dan digital memiliki perbedaan yang signifikan karena sifat operasi yang berbeda. Perbedaan ini memengaruhi strategi penempatan dan perutean komponen.

- Sirkuit Digital: Fokus utama pada kecepatan switching dan minimisasi noise. Penempatan dan perutean komponen didesain untuk meminimalkan delay dan crosstalk antar sinyal.

- Sirkuit Analog: Sensitif terhadap noise dan interferensi elektromagnetik (EMI). Penempatan komponen harus mempertimbangkan kedekatan komponen sensitif, minimisasi loop area, dan pengurangan noise coupling.

Contoh Desain Tata Letak Sirkuit Terpadu Sederhana

Bayangkan sebuah inverter CMOS sederhana. Dua transistor, satu NMOS dan satu PMOS, terhubung secara seri. Transistor NMOS terhubung ke ground, sementara transistor PMOS terhubung ke sumber tegangan. Input diberikan ke gate kedua transistor, dan output diambil dari drain NMOS dan source PMOS. Tata letaknya akan menunjukkan kedua transistor ini yang ditempatkan berdekatan untuk meminimalkan panjang jalur interkoneksi dan mengurangi delay.

Setiap transistor memiliki ukuran geometri tertentu yang ditentukan oleh persyaratan kinerja dan daya. Jalur interkoneksi antara gate, drain, dan source akan dirancang untuk meminimalkan resistansi dan induktansi.

Tantangan dalam Mendesain Tata Letak Sirkuit Terpadu yang Kompleks

Desain tata letak IC modern menghadapi tantangan yang semakin kompleks, seperti meningkatnya kepadatan komponen, kebutuhan untuk mengelola konsumsi daya yang rendah, dan persyaratan kinerja yang tinggi. Penggunaan teknik canggih seperti clock tree synthesis dan power grid optimization menjadi sangat penting untuk memastikan integritas sinyal dan stabilitas sistem.

Perkembangan Teknologi dalam Desain Tata Letak Sirkuit Terpadu

Teknologi desain tata letak IC terus berkembang pesat. Penggunaan Electronic Design Automation (EDA) tools yang canggih memungkinkan desain yang lebih kompleks dan efisien. Teknik-teknik seperti place and route otomatis, verifikasi desain, dan optimasi kinerja telah sangat meningkatkan produktivitas dan kualitas desain. Munculnya teknologi 3D-IC juga membuka kemungkinan untuk meningkatkan kepadatan dan kinerja chip di masa depan.

Implikasi Ekonomi Hak Desain Tata Letak Sirkuit Terpadu

Perlindungan hak desain tata letak sirkuit terpadu (IC layout design) memiliki dampak signifikan terhadap perekonomian, khususnya dalam industri semikonduktor. Sistem hukum yang melindungi desain IC mendorong inovasi, investasi, dan daya saing global bagi perusahaan-perusahaan yang berkecimpung di bidang ini. Dengan mengamankan investasi mereka, perusahaan dapat lebih fokus pada pengembangan teknologi canggih tanpa khawatir akan pembajakan desain.

Dampak Ekonomi Perlindungan Hak Desain IC

Perlindungan hak desain IC memberikan keuntungan ekonomi yang nyata bagi industri semikonduktor. Perusahaan dapat memperoleh keuntungan finansial yang signifikan melalui penjualan produk mereka yang dilindungi, mengurangi risiko kerugian akibat pembajakan, dan menarik investasi lebih besar untuk riset dan pengembangan. Hal ini pada akhirnya berkontribusi pada pertumbuhan ekonomi secara keseluruhan dan peningkatan daya saing global.

Peran Hak Desain IC dalam Mendorong Inovasi Teknologi

Dengan adanya perlindungan hukum, perusahaan lebih termotivasi untuk berinvestasi dalam riset dan pengembangan teknologi semikonduktor yang inovatif. Keuntungan finansial yang diproyeksikan dari penjualan produk yang dilindungi hak cipta mendorong perusahaan untuk terus berinovasi dan menciptakan produk-produk yang lebih canggih dan efisien. Inovasi ini pada gilirannya mendorong kemajuan teknologi secara keseluruhan dan memberikan manfaat bagi masyarakat luas.

Peningkatan Nilai Komersial Produk

Perlindungan hak desain IC secara langsung meningkatkan nilai komersial produk semikonduktor. Produk yang dilindungi hak cipta memiliki nilai jual yang lebih tinggi karena memiliki keunggulan kompetitif, yaitu perlindungan dari peniruan. Hal ini memungkinkan perusahaan untuk menetapkan harga yang lebih tinggi dan mendapatkan keuntungan yang lebih besar. Contohnya, perusahaan yang berhasil melindungi desain prosesor canggihnya dapat menikmati margin keuntungan yang lebih tinggi dibandingkan kompetitor yang tidak memiliki perlindungan serupa.

Estimasi Biaya Pendaftaran dan Durasi Perlindungan Hak Desain IC

| Jenis Biaya | Estimasi Biaya | Durasi Perlindungan | Keterangan |

|---|---|---|---|

| Pendaftaran Awal | Rp 5.000.000 – Rp 15.000.000 (estimasi, bervariasi tergantung kompleksitas desain dan kantor paten) | 10 tahun | Biaya dapat bervariasi tergantung pada kompleksitas desain dan layanan yang diberikan oleh kantor paten. |

| Perpanjangan | Rp 2.500.000 – Rp 7.500.000 (estimasi, bervariasi tergantung kantor paten) per periode perpanjangan | 10 tahun (dapat diperpanjang sekali) | Biaya perpanjangan umumnya lebih rendah daripada biaya pendaftaran awal. |

Catatan: Biaya dan durasi perlindungan dapat bervariasi tergantung pada yurisdiksi dan peraturan yang berlaku. Angka-angka di atas merupakan estimasi umum dan mungkin tidak akurat untuk semua kasus.

Perlindungan Investasi Perusahaan

Perlindungan hak desain IC merupakan instrumen penting bagi perusahaan untuk melindungi investasi besar yang telah mereka tanamkan dalam riset dan pengembangan. Dengan melindungi desain IC mereka dari peniruan, perusahaan dapat mengamankan pengembalian investasi mereka dan mencegah kerugian finansial yang signifikan. Ini memungkinkan perusahaan untuk terus berinovasi dan bersaing di pasar global yang kompetitif.

Pertanyaan dan Jawaban

Apa bedanya Hak Desain Tata Letak Sirkuit Terpadu dengan rahasia dagang?

Rahasia dagang melindungi informasi yang bersifat rahasia dan memberikan keunggulan kompetitif, sedangkan Hak Desain Tata Letak Sirkuit Terpadu melindungi desain fisik IC yang terdaftar secara resmi.

Berapa lama proses pendaftaran Hak Desain Tata Letak Sirkuit Terpadu?

Lama proses pendaftaran bervariasi, tergantung pada kelengkapan dokumen dan proses administrasi di kantor terkait. Biasanya memakan waktu beberapa bulan.

Apa yang terjadi jika saya tidak mendaftarkan Hak Desain Tata Letak Sirkuit Terpadu?

Anda kehilangan perlindungan hukum atas desain IC Anda, sehingga pihak lain dapat meniru dan memproduksi tanpa izin.

Apakah perlindungan Hak Desain Tata Letak Sirkuit Terpadu berlaku internasional?

Perlindungan umumnya terbatas pada negara tempat pendaftaran. Perjanjian internasional dapat memperluas perlindungan ke negara lain.